- 您现在的位置:买卖IC网 > Sheet目录3753 > ATMEGA169P-16MCHR (Atmel)MCU AVR 16KB FLASH 16MHZ 64-VQFN

2005 Microchip Technology Inc.

Preliminary

DS41265A-page 141

PIC16F946

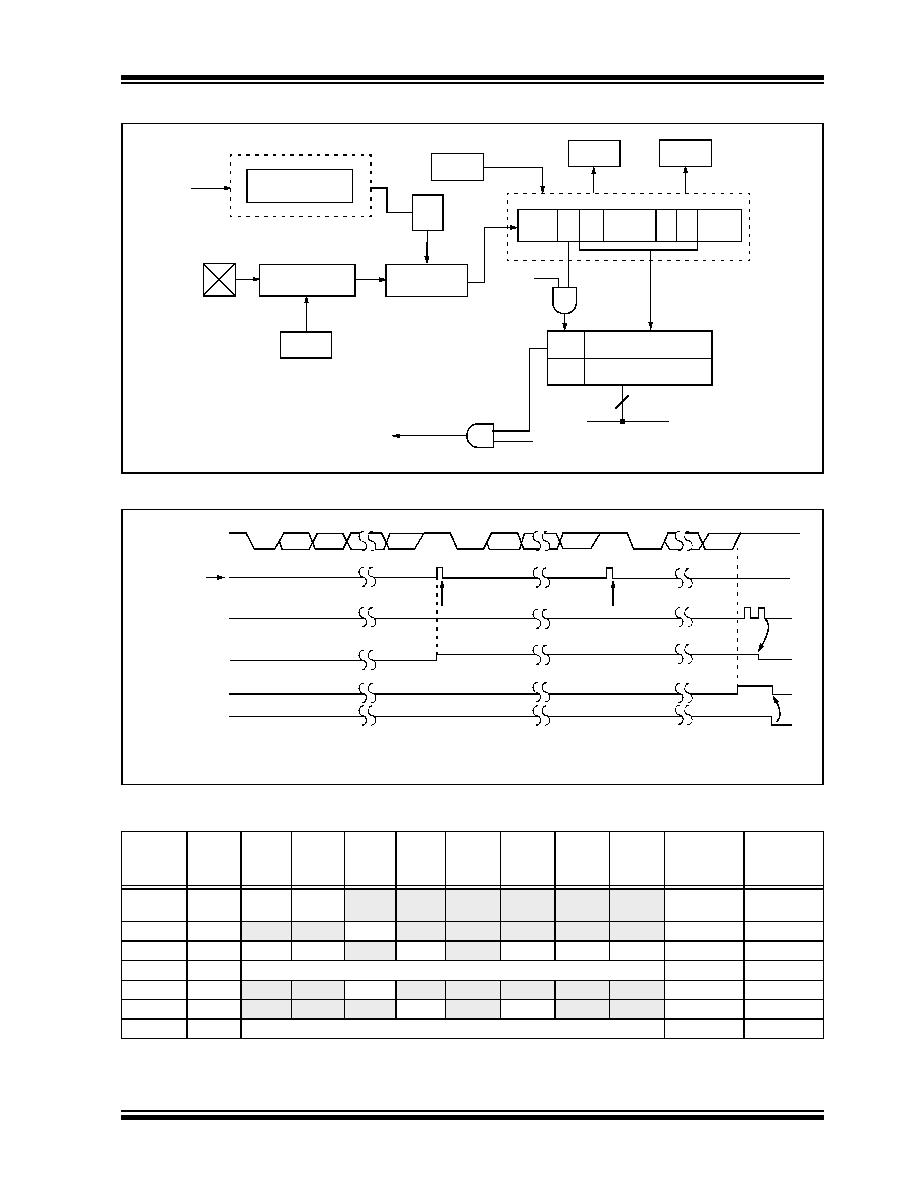

FIGURE 11-4:

USART RECEIVE BLOCK DIAGRAM

FIGURE 11-5:

ASYNCHRONOUS RECEPTION

TABLE 11-6:

REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

Address

Name

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Value on:

POR, BOR

Value on

all other

Resets

0Bh, 8Bh,

10Bh,18Bh

INTCON

GIE

PEIE

T0IE

INTE

RBIE

T0IF

INTF

RBIF

0000 000x

0Ch

PIR1

EEIF

ADIF

RCIF

TXIF

SSPIF

CCP1IF

TMR2IF

TMR1IF

0000 0000

18h

RCSTA

SPEN

RX9

SREN

CREN

ADDEN

FERR

OERR

RX9D

0000 000x

1Ah

RCREG USART Receive Data Register

0000 0000

8Ch

PIE1

EEIE

ADIE

RCIE

TXIE

SSPIE

CCP1IE

TMR2IE TMR1IE

0000 0000

98h

TXSTA

CSRC

TX9

TXEN

SYNC

—BRGH

TRMT

TX9D

0000 -010

99h

SPBRG

Baud Rate Generator Register

0000 0000

Legend:

x

= unknown, – = unimplemented locations read as ‘0’. Shaded cells are not used for asynchronous reception.

x64 Baud Rate CLK

SPBRG

Baud Rate Generator

RC7/RX/DT/

Pin Buffer

and Control

SPEN

Data

Recovery

CREN

OERR

FERR

RSR Register

MSb

LSb

RX9D

RCREG Register

FIFO

Interrupt

RCIF

RCIE

Data Bus

8

÷64

÷16

or

Stop

Start

(8)

7

1

0

RX9

FOSC

SDI/SDA/SEG8

Start

bit

bit 7/8

bit 1

bit 0

bit 7/8

bit 0

Stop

bit

Start

bit

Start

bit

bit 7/8

Stop

bit

RX (pin)

Reg

Rcv Buffer Reg

Rcv Shift

Read Rcv

Buffer Reg

RCREG

RCIF

(Interrupt Flag)

OERR bit

CREN

Word 1

RCREG

Word 2

RCREG

Stop

bit

Note:

This timing diagram shows three words appearing on the RX input. The RCREG (Receive Buffer) is read after the third word,

causing the OERR (Overrun Error) bit to be set.

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

2-1546217-0

TERM BLK RCPT 20POS SIDE 5.08MM

1-1546217-9

TERM BLK RCPT 19POS SIDE 5.08MM

1-1546217-8

TERM BLK RCPT 18POS SIDE 5.08MM

1-1546217-7

TERM BLK RCPT 17POS SIDE 5.08MM

1-1546217-6

TERM BLK RCPT 16POS SIDE 5.08MM

1-1546217-5

TERM BLK RCPT 15POS SIDE 5.08MM

1-1546217-4

TERM BLK RCPT 14POS SIDE 5.08MM

1-1546217-3

TERM BLK RCPT 13POS SIDE 5.08MM

相关代理商/技术参数

ATMEGA169P-16MCU

功能描述:8位微控制器 -MCU AVR 16KB, 512B EE 16MHz 1KB SRAM, 5V

RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

ATMEGA169P-16MU

功能描述:8位微控制器 -MCU AVR 16K FLASH 512B EE 1K SRAM LCD ADC RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

ATMEGA169P-16MU SL383

制造商:Atmel Corporation 功能描述:MCU 8BIT ATMEGA RISC 16KB FLASH 3.3V/5V 64PIN MLF - Tape and Reel

ATMEGA169P-16MUR

功能描述:8位微控制器 -MCU AVR LCD 16KB FLSH EE 512B 1KB SRAM-16MHZ RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

ATMEGA169P-8AU

制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:Microcontroller with 16K Bytes In-System Programmable Flash

ATMEGA169P-8MU

制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:Microcontroller with 16K Bytes In-System Programmable Flash

ATMEGA169PA

制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:8-bit Microcontroller with 16K Bytes In-System Programmable Flash

ATMEGA169PA_1

制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:High Endurance Non-volatile Memory segments